Los chips emblemáticos funcionan mal, esta “olla” no puede simplemente dejar que Samsung regrese

Incluso si no eres un entusiasta de la electrónica de consumo, debes conocer el tallo del "dragón de fuego" en los últimos dos años.

▲ Imagen de: "Juego de Tronos"

La razón principal es que en las últimas generaciones de chips emblemáticos de Android, el consumo de energía se ha "transferido" uno tras otro. El alto rendimiento suele ir acompañado de un alto consumo de energía, que también va acompañado de un fuerte aumento del calor del teléfono móvil.

Esto trae una ventaja y una desventaja. La ventaja es que los fabricantes obtienen niveles cada vez más altos de "disipación de calor", mientras que la desventaja es que el ajuste del chip se vuelve más conservador, así como una pared de control de temperatura más baja.

Bajo el apretón continuo de alto rendimiento (como ejecutar "Yuan Shen"), básicamente en 10 ~ 15 minutos, los productos reducirán activamente la frecuencia del súper núcleo del chip. Si la temperatura sigue siendo alta, el siguiente límite es el gran centro.

Por otro lado, al usar chips emblemáticos con tecnología más avanzada, en condiciones diarias, debería haber una mejora en la duración de la batería.

Sin embargo, en uso, la mejora de la duración de la batería es "rociar agua", que tiene poco efecto y depende de una carga rápida de alta potencia para continuar la vida.

Además, hay otro punto, la reciente inestabilidad del proceso de 4nm en la fundición de Samsung puede considerarse como una razón. Su propio chip insignia Exynos 2200 también ha tenido un rendimiento inferior, no intencionalmente.

Como resultado, Qualcomm, que se vio "profundamente afectada", también anunció el uso del proceso de 4 nm de TSMC en el SoC Snapdragon 8+ Gen1 recién anunciado , y declaró directamente en el PPT que el rendimiento mejoró en un 10 % y el consumo de energía. se redujo en un 30%.

Parece que el bajo rendimiento de los chips insignia de Android se debe a que el proceso de 4nm de Samsung es "demasiado malo", ¿entonces TSMC es un "rescate"?

El 4nm de TSMC es solo una "tela de figura"

TSMC y Samsung son casi los dos principales oligarcas en la producción de chips de procesos avanzados del mundo. Los dos casi dominan el mercado mundial de chips producidos por debajo de 10nm.

▲ Imagen de: wccftech.com

En unos años, de 10nm a 4nm, y también están construyendo líneas de producción y fundiciones de 3nm, la competencia se está intensificando.

A diferencia de la fundición pura de TSMC, Samsung es una empresa de fabricación integrada verticalmente (IDM) que integra chips de diseño independientes, chips de producción y chips propios de Exynos.

Hace 10 años, Samsung quería estar por delante de TSMC, y el chip A4 de Apple también fue modificado mágicamente de Samsung Exynos, y fue fabricado por él.

Debido a la identidad especial de Samsung y al hecho de que la pantalla y la memoria dependen de Samsung, el riesgo es demasiado alto y Apple comenzó a respaldar a TSMC para transferir el riesgo.

Después de giros y vueltas, TSMC construyó una nueva línea de producción, asignó un equipo profesional y finalmente ganó la fundición exclusiva del chip A8 de Apple. Junto con las ventas sin precedentes del iPhone 6 y 6 Plus, TSMC se ha beneficiado mucho de ello.

Posteriormente, los chips de la serie A de Apple comenzaron a vincularse con TSMC y ayudaron a su desarrollo a través de la inclinación de recursos. Hoy en día, los chips de la serie A y la serie M de Apple son todos fundidos por TSMC, y se han convertido en los clientes de mayor prioridad, ninguno de ellos.

▲ TSMC y Apple están profundamente unidos Imagen de: appuals.com

Al mismo tiempo, se ha creado el "mito" de la alta estabilidad de la fundición de chips TSMC.

Tanto el 5nm como el 4nm van a la zaga del Samsung de TSMC, y no se desalientan, pero tienen un semental. Anunció una inversión de 133 billones de wones (alrededor de 800 mil millones de yuanes), con el objetivo de lograr el proceso de 3 nm y, por lo tanto, convertirse en el fabricante de SoC más grande del mundo.

▲ Imagen de: Samsung

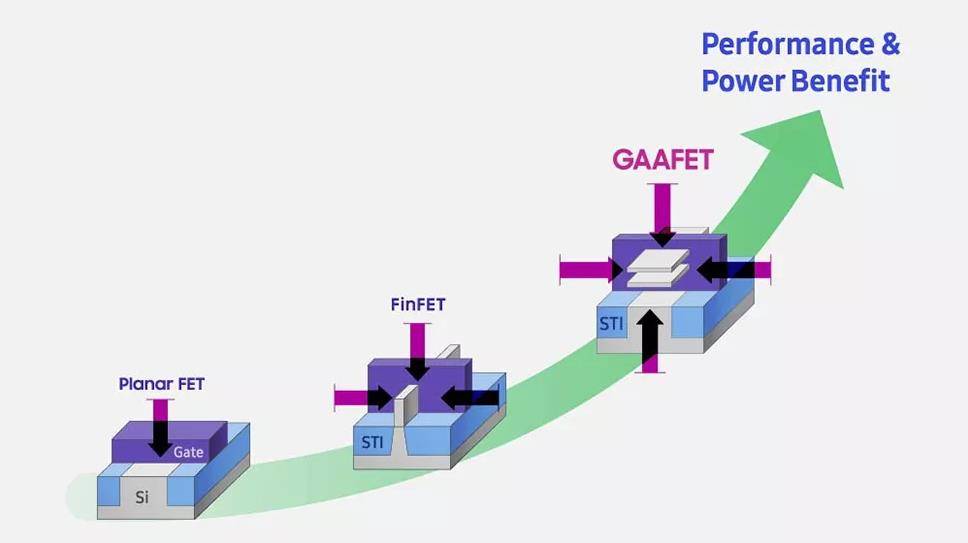

Y, abandonando la tecnología FinFEET, pero un paso hacia la tecnología de transistores GAAFET, para lograr la superación de TSMC, el éxito o el fracaso están aquí.

Volviendo al presente, la densidad de obleas de 5nm y 4nm de Samsung y la estabilidad del proceso no son tan buenas como las de TSMC, por lo que existe una cierta brecha cuando se retroalimenta al chip insignia.

MediaTek Dimensity 9000 a principios de este año utiliza el proceso de 4nm de TSMC, el núcleo ultragrande Cortex-X2 (3,05 GHz), el núcleo grande A710 (2,85 GHz) y el núcleo medio A510 (1,8 GHz) en el 1+ 3+4 arquitectura de tres clústeres. ) son mucho más altas que Qualcomm Snapdragon 8 Gen1.

En teoría, tiene un mayor rendimiento y una mejor eficiencia energética, lo que lo convierte en un chip insignia perfecto.

Sin embargo, después de esperar unos meses, cuando se lanzan los buques insignia equipados con Dimensity 9000 , el rendimiento de eficiencia energética real en realidad no es muy diferente de la versión de Qualcomm. Si no compara con cuidado, es posible que no lo note en absoluto. .

En esta promoción de alto perfil de Qualcomm, cuando el Snapdragon 8+ Gen1 que utiliza el proceso de 4 nm de TSMC tendrá un mejor rendimiento, en realidad no tenía grandes expectativas.

▲ Después del lanzamiento de Snapdragon 8+ Gen1, la "Supercopa" de muchos fabricantes también regresará, y se acerca lo más destacado.

En vista del overclocking integral de Snapdragon 8+ Gen1 (Cortex-X2 3.2GHz + A710 2.75GHz + A510 2.0GHz), el rendimiento absoluto mejorará. En cuanto a la mejora, depende del ajuste de los fabricantes, y lo mismo es cierto para la eficiencia energética.

De esta manera, la tecnología de proceso de 4nm de TSMC es más como una "tela de higo" para los chips emblemáticos, que cubre la nueva arquitectura de la versión pública extremadamente débil de Arm.

La arquitectura de la versión pública de Arm es el "culpable"

En los últimos diez años, Arm ha cambiado 9 versiones de la arquitectura, y la última Armv9 es una actualización relativamente importante del conjunto de instrucciones.

Con la actualización del conjunto de instrucciones, Arm también anunció la versión pública de la CPU IP, que es el núcleo súper grande Cortex-X2, el núcleo grande (núcleo de rendimiento) Cortex-A710 y el núcleo medio (núcleo de rendimiento) Cortex-A510 .

▲ Imagen de: Brazo

La versión pública de la arquitectura de la CPU todavía usa la arquitectura de tres plex, es decir, 1+3+4. Es una evolución de la arquitectura big.LITTLE anterior. El propósito no es más que "el núcleo correcto para el trabajo correcto" para mejorar la eficiencia energética.

La arquitectura mixta de núcleos grandes y pequeños ahora se usa ampliamente en CPU de escritorio y móviles de arquitecturas X86 y Arm.

▲ Intel 12 también adopta la arquitectura híbrida de P+E.

La versión pública de Arm de la arquitectura de tres clústeres, si cada uno realiza sus propias tareas, el X2 de núcleo ultragrande proporciona un rendimiento absoluto, el A710 de núcleo grande comparte los requisitos de rendimiento diarios y el A510 de núcleo medio completa las tareas correspondientes con bajo consumo de energía. consumo.

Los tres núcleos, cada uno con su propio propósito, deben estar inclinados en diseño e invocación.

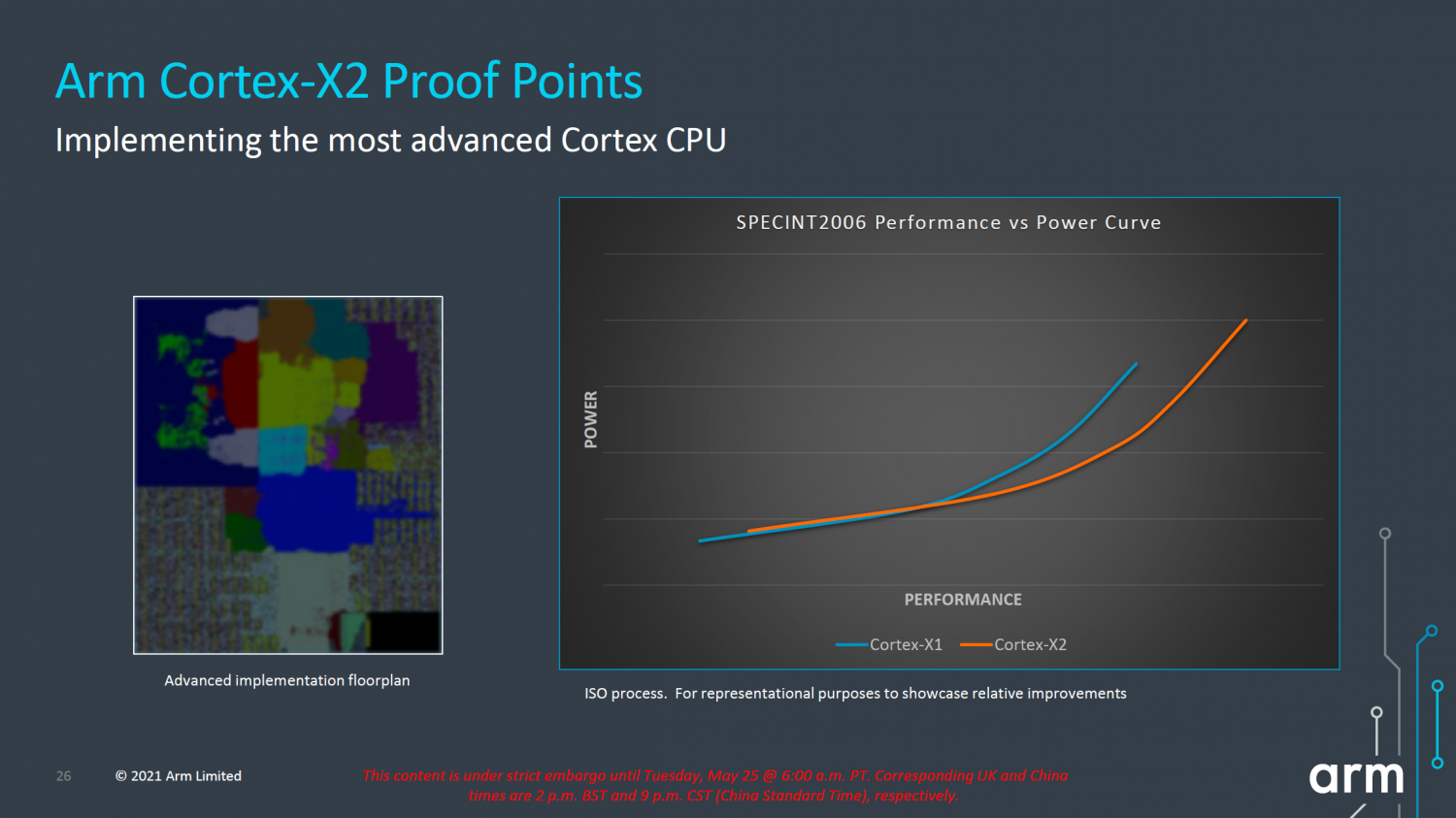

Cortex-X2, que es una versión completamente optimizada de X1, duplica el caché L3 a 8 MB, aumenta el área de caché, optimiza el retraso de la comunicación y obtiene una mejora de IPC del 16% (rendimiento también comprensible).

▲ El núcleo súper grande ha mejorado significativamente.Imagen de: Arm

De los productos de seguimiento, Snapdragon 8Gen1 y Dimensity 9000 tienen un mejor rendimiento que Snapdragon 888 cuando el rendimiento está completamente encendido y el consumo de energía no "explota".

Es razonable cambiar un alto consumo de energía por un alto rendimiento.

Pero el núcleo grande y el núcleo medio tienen grandes problemas, y son estos dos núcleos con nuevos "nombres" los que hacen que los chips insignia se desplacen con frecuencia.

Cortex-A710 no usa una arquitectura más nueva, sigue siendo la optimización del clásico A78, y puede ser más exacto llamarlo A79.

Anandtech llamó a este nuevo nombre "un dato de marketing interesante", y el rendimiento del A710 es evidente.

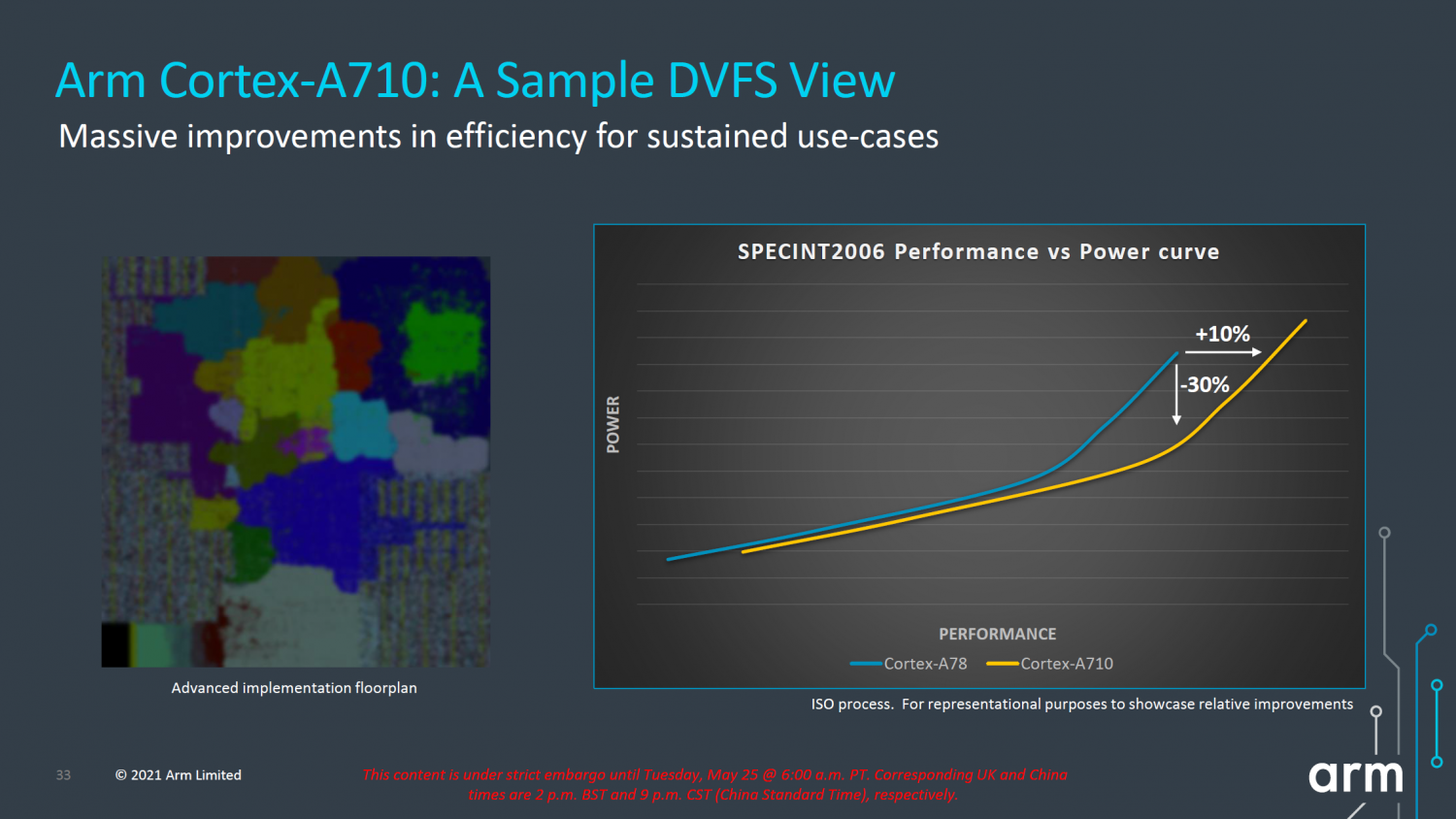

▲ Alto consumo energético y alto rendimiento Imagen de: Arm

En el PPT de Arm, el A710 tiene una mejora del rendimiento del 10 %, al mismo tiempo que optimiza la eficiencia energética en un 30 %. Sin embargo, desde el punto de vista de la curva, el mayor rendimiento se ubica mayoritariamente en la parte de alto consumo de energía, y se obtiene al duplicar el caché L3 (8MB).

La optimización de la eficiencia energética solo reduce el rendimiento de distribución del núcleo A710 (de 6 a 5), no de la optimización de la arquitectura.

▲ No imitar Imagen de: tenor

El A710 es una versión optimizada del A78 y el A78 es una versión overclockeada del A77. Durante algunos años, el equipo de diseño del gran núcleo de Arm todavía está explorando el potencial de la arquitectura A77, pero después de que el A78 alcanza la frecuencia óptima de la arquitectura, la relación de eficiencia energética del A710 es increíble, especialmente cuando el sistema necesita un alto rendimiento. pero no es suficiente para cambiar al X2 ultra grande. Cuando se usa el núcleo, el consumo de energía despega directamente.

Incluso, Arm usa directamente el A78 de 4 nm con el núcleo ultra grande X2, que puede tener mejores resultados.

Como gran núcleo, el A710 necesita más rendimiento que un diseño de eficiencia energética El brazo está en la dirección equivocada.

▲ A510 de nuevo diseño Imagen de: Arm

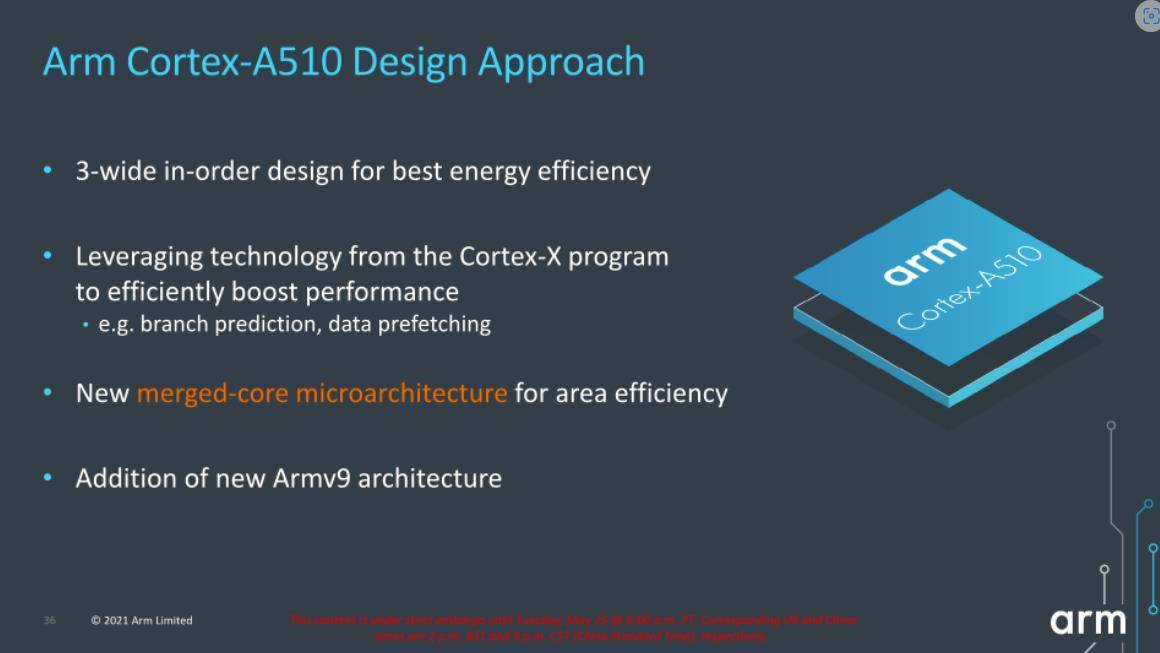

En términos relativos, el núcleo del Cortex-A510 es una nueva arquitectura de diseño. Y a diferencia del equipo de Austin que diseñó los dos núcleos de X2 y A710, fue diseñado por el equipo de Cambridge.

La arquitectura A510 adopta muchas ideas de diseño innovadoras, como el uso de "hiper-threading" para compartir el caché L2 y, al mismo tiempo, el ancho de banda L1, L2 y L3 aumenta al doble que el A55, mejorando así el rendimiento de punto flotante en un 50 % y las operaciones con enteros también tienen una mejora del 35 %.

Sin embargo, el A510 aún usa la "ejecución secuencial" en lugar de la "ejecución fuera de orden" de los núcleos de bajo consumo en los chips de la serie A de Apple. Para evitar la latencia de las instrucciones, se aumentó la parte frontal del A510, se duplicó el caché y se amplió la parte trasera.

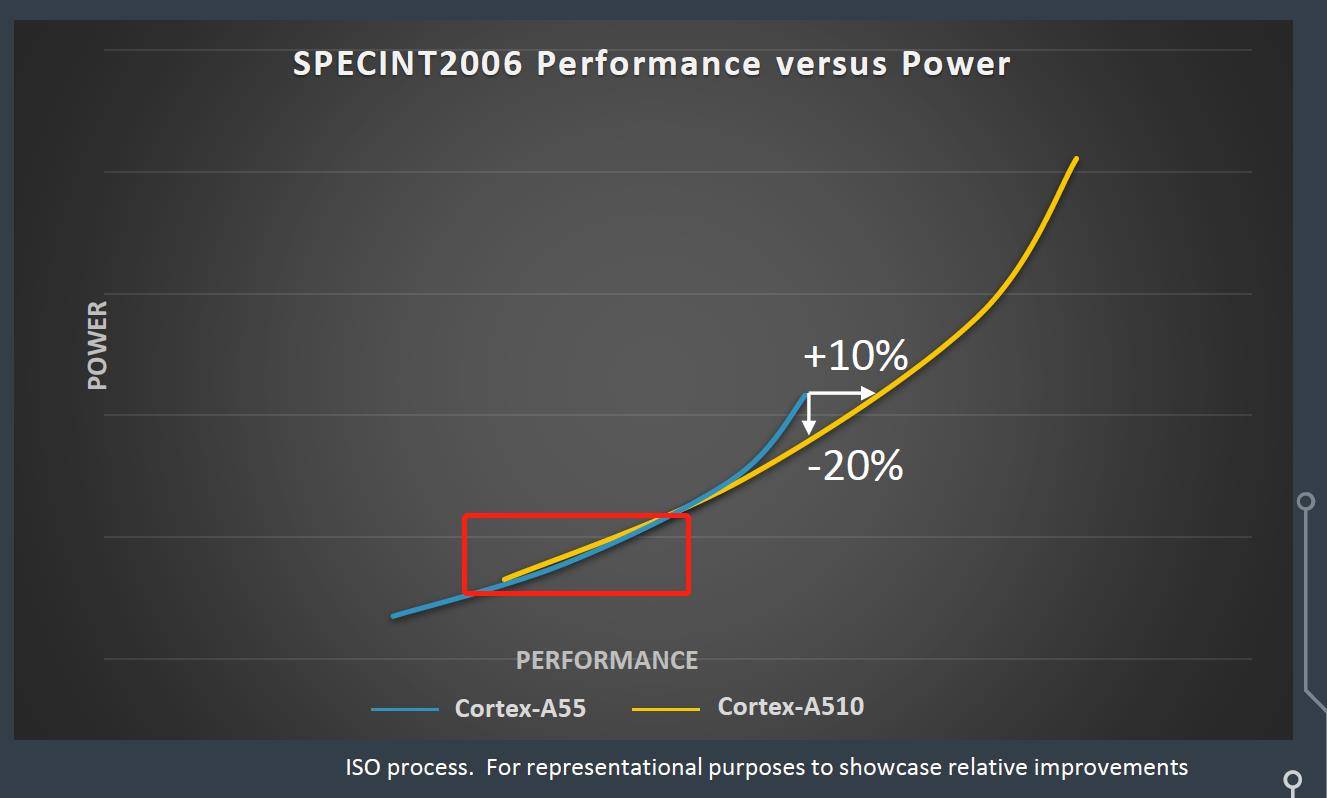

▲ Un brazo honesto, tenga en cuenta que el eje vertical es el consumo de energía.Imagen de: Brazo

La idea de diseño también es relativamente clara, solo para un mejor "rendimiento". Sólo el resultado final, pero con poco éxito.

Desde Arm's PPT, el A510 solo puede obtener un mejor rendimiento que el A55 en el caso de un alto consumo de energía.

Sin embargo, en términos de bajo consumo de energía, que es el foco del núcleo de eficiencia energética, es difícil abrir la brecha con el A55, e incluso hay algunos "retrocesos".

▲ No imitar Imagen de: tenor

En general, entre las arquitecturas de tres clústeres que Arm ha presentado en los últimos años, solo el núcleo ultragrande Cortex-X2 es un cambio relativamente normal. El Cortex-A710 de núcleo grande se centra en la eficiencia energética, mientras que el Cortex-A710 de núcleo medio A510 ha comenzado a centrarse en el máximo rendimiento.

La versión pública de Arm de la IP de la CPU sigue siendo así, así que no espere que el chip insignia se modifique sobre esta base, lo bueno que puede ser el rendimiento.

Si no quieres abrazar el ecosistema de aplicaciones de 64 bits de las grandes fábricas, tienes que salir y tomar la "olla".

Después del lanzamiento de Armv9, el mayor cambio es abandonar por completo las aplicaciones de 32 bits y adoptar por completo las aplicaciones de 64 bits.

En otras palabras, en la arquitectura de tres clústeres, en teoría, todos los núcleos ya no admiten aplicaciones de 32 bits, pero para el entorno de aplicaciones de Android en el mercado chino, Arm ha aprobado especialmente los núcleos del A710 para que sean compatibles con 32 bits. aplicaciones de bits.

Es decir, cuando abres una app de 32 bits, obligará a que el A710, un núcleo de alto consumo energético, permanezca activo, aunque solo apagues la pantalla para escuchar una canción.

De hecho, desde Armv8, Arm ha estado promocionando aplicaciones de 64 bits, y Google Store también estipuló que los nuevos programas deben admitir aplicaciones de 64 bits en agosto de 2019.

Sin embargo, muchos fabricantes de aplicaciones nacionales no han realizado mejoras. Muchas aplicaciones de uso común, como Alipay, QQ y NetEase Cloud, todavía son de 32 bits y no hay planes para cuándo se lanzará la versión de 64 bits.

Además, las tiendas de software de muchos fabricantes nacionales de Android no tienen particiones de aplicaciones de 64 bits correspondientes, y las aplicaciones de 32 y 64 bits están mezcladas.

Sin embargo, OPPO, vivo y Xiaomi ya han comenzado a popularizar las aplicaciones de 64 bits. La primera etapa es restringir las aplicaciones recién lanzadas para que sean de 64 bits. En cuanto a las aplicaciones de uso común, por el momento no se han publicado medidas relevantes.

En los últimos años, los chips emblemáticos de Android han encontrado problemas con frecuencia. La razón más fundamental es que la dirección de diseño de la arquitectura de la versión pública de Arm viola la intención original de la arquitectura de tres clústeres, y los fabricantes nacionales no adoptan activamente las aplicaciones de 64 bits. .

En cuanto a si es TSMC o Samsung, Dimensity o Qualcomm, en el lado del dispositivo, la diferencia entre ellos es mucho menor que los números en el PPT.

#Bienvenido a prestar atención a la cuenta oficial de WeChat de Aifaner: Aifaner (WeChat: ifanr), se le brindará más contenido emocionante lo antes posible.